# Analysis of Resistance and Mobility in InGaAs Quantum-Well MOSFETs From Ballistic to Diffusive Regimes

Jianqiang Lin, *Member, IEEE*, Yufei Wu, Jesús A. del Alamo, *Fellow, IEEE*, and Dimitri A. Antoniadis, *Life Fellow, IEEE*

Abstract—Recent advances in the fabrication technology have yielded nanometer-scale InGaAs quantum-well (QW) MOSFETs with extremely low and reproducible external contact and access region resistances. This allows, for the first time, a detailed analysis of the role of ballistic transport in the operation of these devices. This paper presents a systematic analysis of external resistance, ballistic resistance, and channel mobility in InGaAs QW-MOSFETs under near-equilibrium conditions, i.e., under very low drain-source bias. This is an important regime for device characterization. Devices with a wide range of channel lengths, from 70 to 650 nm, are investigated. Our analysis includes the consideration of the impact of carrier degeneracy in the QW channel. We show that unless the ballistic behavior in the intrinsic channel is accounted for, the standard extraction technique for external resistance grossly exaggerates its value as it incorporates the so-called ballistic resistance. By separating out the ballistic resistance, the external resistance in our devices is shown to be extremely low, 74  $\Omega$ - $\mu$ m, including both source and drain sides. This is thanks to our contact-first self-aligned Mo-contact technology. Furthermore, taking the advantage of the wide range of ballisticity of the devices studied in this paper, we demonstrate a methodology to self-consistently extract scattering-dependent effective mobility, mean-free-path length, and ballistic mobility.

Index Terms—III-V, ballistic mobility, ballistic resistance, near-equilibrium transport, quantum-well (QW) MOSFETs.

# I. INTRODUCTION

InAs-RICH InGaAs is a promising channel material for future CMOS applications due to its superior electron transport properties. In the last few years, there have been significant research efforts toward developing the InGaAs MOSFET technology and unprecedented transistor performance has been demonstrated recently [1]–[3]. InGaAs quantum-well (QW) MOSFETs with a record transconductance,  $g_m$ , of 3.1 mS/ $\mu$ m were demonstrated by our group

Manuscript received December 29, 2015; revised February 6, 2016; accepted February 16, 2016. Date of publication March 7, 2016; date of current version March 22, 2016. This work was supported jointly by the Defense Threat Reduction Agency under Contract HDTRA 1-14-1-0057, the National Science Foundation through the NCN-NEEDS Program under Grant 1227020-EEC, and the National Science Foundation through the Center for Energy Efficient Electronics Science Center under Award 0939514. The review of this paper was arranged by Editor G. Meneghesso.

The authors are with Microsystems Technology Laboratories, Massachusetts Institute of Technology, Cambridge, MA 02139 USA (e-mail: linjq@mit.edu). Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2016.2532604

in 2014 using a self-aligned recessed-gate technology [4]. The excellent ON-state performance of these devices arises from our emphasis on minimization of external resistance through self-aligned design and very low contact resistivity of the source and drain contacts.

When the channel length of an MOSFET is comparable with or smaller than the mean-free-path (MFP), near-ballistic transport is to be expected. In InGaAs high-electronmobility transistors (HEMTs), the MFP of 194 nm has been extracted [5]. Assuming comparable MFP, in nanometer-scale InGaAs QW-MOSFETs with very low parasitics, the signature of ballistic transport should clearly emerge, even at room temperature. At low electric field, ballistic transport manifests itself in a length-independent channel resistance or, equivalently, a length-dependent carrier mobility. This effect is explained using the concepts of ballistic resistance [6]-[8] or ballistic mobility [9]-[11]. The ballistic resistance has a strong dependence on the 2-D carrier concentration  $(N_s)$ . This has already been observed in very short-channel Si fully-depleted silicon-on-insulator MOSFETs [12]. Similar studies have yet to be carried out in InGaAs MOSFETs even though with gate lengths in the sub-100 nm regime, these devices should be operating closer to the ballistic limit than equivalent Si MOSFETs. Part of the reason for the absence of such studies is the requirement that the external resistance should be small and exhibits a consistent value from device to device.

In this paper, for the first time, we have carried out extensive characterization of well-behaved InGaAs QW-MOSFETs with a total external resistance below  $100~\Omega$ - $\mu$ m. We have measured devices over a broad range of gate lengths with the goal of studying electron transport from near-ballistic to near-diffusive regimes. Our work reveals the important roles of ballistic resistance and ballistic mobility in high-performance InGaAs transistors. Our results clearly show that in these devices, quantum-mechanical ballistic transport phenomena must be taken into account for proper device characterization and modeling to be performed. Furthermore, our study reveals that channel carrier degeneracy must be accounted for even at moderate gate overdrive. This is the result of the relatively low density of states of the InGaAs channel.

This paper is organized as follows. Section II describes the device structure used in this paper. Section III extracts and analyzes the experimental channel and external

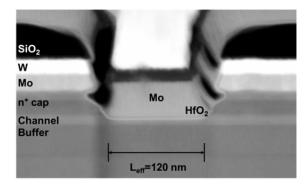

Fig. 1. TEM cross section of a QW InGaAs MOSFET similar to those used in this paper.  $L_{\rm eff}$  is defined as the length of the flat portion of the gate directly above the channel.

resistances and explains the importance of ballistic resistance. Section IV extracts the apparent mobility by the split capacitance–voltage (C–V) method. From this, MFP, long-channel scattering-limited effective field mobility, and ballistic mobility are extracted self-consistently and their dependencies on gate length and degeneracy are investigated. The conclusion is drawn in Section V.

## II. DEVICE DESCRIPTION

The devices used in this paper and their fabrication processes have been discussed elsewhere [4], [13]. In essence, this is a contact-first self-aligned architecture, in which the channel is recessed using the ohmic contacts as a mask. The gate recess consists of a combination of dry etch and self-limiting digital etch to precisely control the critical dimensions in both the lateral and vertical directions of the device [14]. In particular, our fabrication process yields a channel thickness control in the scale of  $\sim$ 1 nm.

An example of a device used in this paper is shown in the cross-sectional transmission electron micrograph (TEM) in Fig. 1. This device features an effective gate length,  $L_{\rm eff}$ , of 120 nm. The access regions that link the W/Mo contacts to the channel are each 15 nm long and are covered by an  $n^+$  InGaAs/InP cap which makes them highly conducting. The gate insulator consists of 2.5 nm HfO2 that conformably covers the gate and access regions. The gate metal is also Mo. To help reduce the device access resistance, a slight overlap is created between the gate and the  $n^+$  cap at the edge of the access region. Through process optimization, our gate recess yields a smooth and uniform channel, as shown in Fig. 1. The channel thickness of all devices in his paper is estimated to be 7 nm (different from Fig. 1). The channel consists of 2 nm InAs on the top of 5 nm In $_{0.7}$ Ga $_{0.3}$ As.

Devices with  $L_{\rm eff}$  between 70 and 650 nm have been studied.  $L_{\rm eff}$  is the effective gate length estimated from the printed gate length by electron-beam lithography and calibration from cross-sectional TEM images. All device measurements have been taken at room temperature.

#### III. ANALYSIS OF RESISTANCE

The linear-regime transfer characteristics of InGaAs MOSFETs with  $L_{\rm eff}$  from 70 to 650 nm are measured

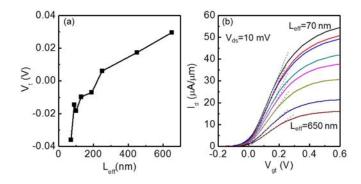

Fig. 2. (a) Linear threshold voltage as a function of  $L_{\rm eff}$  obtained at  $V_{\rm ds} = 10$  mV. (b) Linear-regime transfer characteristics versus gate overdrive,  $I_d$ – $V_{\rm gt}$ , at  $V_{\rm ds} = 10$  mV. Respective  $L_{\rm eff}$  values from top to bottom are 70, 90, 100, 130, 190, 250, 450, and 650 nm.

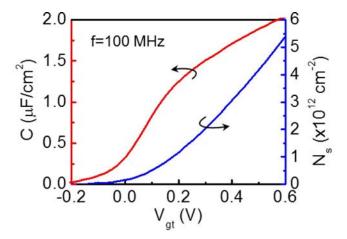

Fig. 3. Capacitance and integrated charge density versus  $V_{\rm gt}$  of a 1  $\mu \rm m$  by 10  $\mu \rm m$  device. The split C–V measurement was carried out at a frequency of 100 MHz. Drain and source contacts are shorted together.

at  $V_{\rm ds}=10$  mV. We find that the threshold voltage,  $V_t$ , changes with  $L_{\rm eff}$  as a result of short-channel effects [Fig. 2(a)].  $V_t$  is determined by extrapolating from the maximum slope (maximum  $g_m$  point) of the linear transfer characteristics to  $I_d=0$ . Typical transfer characteristics versus gate overdrive,  $V_{\rm gt}=V_{\rm gs}-V_t$ , for  $V_{\rm ds}=10$  mV are plotted in Fig. 2(b).

The C–V characteristics were also measured using the split C–V method on a device with a gate length of 1  $\mu$ m and width of 10  $\mu$ m at  $V_{\rm ds}=0$  V. A relatively high frequency of 100 MHz has been used to diminish the influence of interface states, but little frequency dispersion was observed above 1 MHz (not shown here). Gate overlap capacitance obtained at  $V_{\rm gt}=-0.3$  V is subtracted from the measured capacitance. The result is shown in Fig. 3. The channel electron sheet density is obtained by integrating the capacitance, and is shown in the same plot.

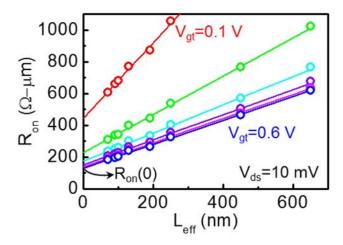

The ON-resistance of the MOSFETs under varying gate overdrive was also extracted as  $R_{\rm ON} = V_{\rm ds}/I_d$  for  $V_{\rm ds} = 10$  mV, and is shown in Fig. 4.  $R_{\rm ON}(0)$  is extracted by extrapolating the linear fit of  $R_{\rm ON}$  versus  $L_{\rm eff}$  to  $L_{\rm eff} = 0$ . The least-square method is applied to all linear fits in this paper. The excellent fits that are obtained illustrate the consistent

Fig. 4.  $R_{\rm ON}$  versus  $L_{\rm eff}$  under different  $V_{\rm gt}$ .  $R_{\rm ON}(0)$  is extracted from the  $R_{\rm ON}$ -axis intersect of fitted straight lines.

value of external resistance in these devices.  $R_{\rm ON}(0)$  is usually referred to as  $R_{\rm SD}$ , and is typically attributed to the external resistance of all devices, which is common to all of them and independent of gate length. As we shown below, this interpretation is erroneous under prominent ballistic transport conditions.

In the long-channel devices, the slope of  $R_{\rm ON}$  versus  $L_{\rm eff}$  is known to be inversely proportional to the channel carrier mobility. However, in devices operating in the near-ballistic regime, this interpretation of mobility requires care. It is well known that with prominent ballistic effects, this mobility is the apparent channel mobility,  $\mu_{\rm app}$ , which is given by Matthiessen's law [10], [15]

$$\frac{1}{\mu_{\text{app}}} = \frac{1}{\mu_{\text{eff}}} + \frac{1}{\mu_{B}}.\tag{1}$$

In (1),  $\mu_{\rm eff}$  is the scattering-limited carrier (effective) mobility, or diffusive mobility, i.e., the one that would be measured in very long-channel devices under purely diffusive transport.  $\mu_B$  is the ballistic mobility [10], [16], which represents the finite velocity that an electron at rest can acquire in a short, purely ballistic channel under the influence of a small electric field. In a 2D system,  $\mu_B$  is given by [15], [16]

$$\mu_B = \frac{\nu_{T0}}{2\phi_T} \frac{L_{\text{eff}} \mathscr{F}_{-1/2}(\eta)}{\mathscr{F}_0(\eta)} \tag{2}$$

where  $v_{T0}$  is the nondegenerate unidirectional thermal velocity in the 2DEG,  $\phi_T$  is the thermal voltage,  $k_BT/q$ ,  $\mathscr{F}_j$  is the Blakemore Fermi–Dirac integral of order j, and  $\eta$  is the reduced surface potential.

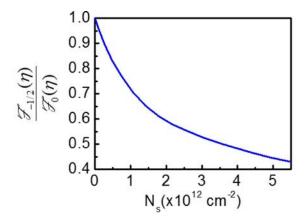

The ratio of the Fermi integrals in (2) accounts for channel carrier degeneracy at high carrier density,  $N_s$ , i.e., high values of  $V_{\rm gt}$  and, therefore,  $\eta$ . For small values of  $\eta$ , this ratio goes to 1, as shown in Appendix A.

It can also be shown (Appendix A) that the scatteringlimited mobility can generally be written as

$$\mu_{\text{eff}} = \frac{\nu_{T0}}{2\phi_T} \frac{\lambda \mathscr{F}_{-1/2}(\eta)}{\mathscr{F}_0(\eta)} \tag{3}$$

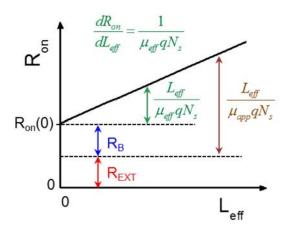

Fig. 5. Plot of  $R_{\rm ON}$  versus  $L_{\rm eff}$  at a given gate overdrive illustrating different components of  $R_{\rm ON}$  and its overall linear dependence on  $L_{\rm eff}$ . The slope of  $R_{\rm ON}$  versus  $L_{\rm eff}$  is linearly proportional to  $1/\mu_{\rm eff}$ , but is not proportional to  $1/\mu_{\rm app}$  (see text).

where  $\lambda$  is the carrier MFP which in general also depends on carrier concentration.

The ON-resistance for a given device is given as

$$R_{\rm ON} = R_{\rm EXT} + \frac{L_{\rm eff}}{\mu_{\rm app} q N_s}.$$

(4)

Inserting (1) and (2) into (4), we obtain

$$R_{\rm ON} = R_{\rm EXT} + \frac{2\phi_T}{v_{T0}qN_s} \frac{\mathscr{F}_0(\eta)}{\mathscr{F}_{-1/2}(\eta)} + \frac{L_{\rm eff}}{\mu_{\rm eff}qN_s}.$$

(5)

The extrapolation of this expression to  $L_{\text{eff}} = 0$  yields  $R_{\text{ON}}(0)$ , which is given by

$$R_{\rm ON}(0) = R_{\rm EXT} + R_B. \tag{6}$$

$R_{\rm ON}(0)$  is the sum of the external resistance  $R_{\rm EXT}$ , also known as parasitic resistance, plus a second term which accounts for ballistic transport in the channel, and is known as the ballistic resistance,  $R_B$ , as discussed in Section I.  $R_B$  is given by

$$R_B = \frac{2\phi_T}{v_{T0}qN_s} \frac{\mathscr{F}_0(\eta)}{\mathscr{F}_{-1/2}(\eta)}.$$

(7)

Fig. 5 shows (5) in graphical form. The straight line is the total ON-resistance as a function of  $L_{\rm eff}$  at the same  $V_{\rm gt}$ , or  $N_s$ . The slope of  $R_{\rm ON}$  versus  $L_{\rm eff}$  is linearly proportional to  $1/\mu_{\rm eff}$ , but is not proportional to  $1/\mu_{\rm app}$  due to the presence of ballistic mobility or, equivalently, ballistic resistance. The proportionality is shown in the equation in Fig. 5 (inset).  $R_{\rm ON}(0)$  is the y-intersection of  $R_{\rm ON}$  versus  $L_{\rm eff}$ , which is the sum of  $R_B$  and  $R_{\rm EXT}$ .

Our experimental results in Fig. 4(a) exhibit a similar linear dependence of  $R_{\rm ON}$  versus  $L_g$  consistent with this theory. It is also observed that  $R_{\rm ON}(0)$  and the slope of the linear dependence both decrease as  $V_{\rm gt}$  is increased. We analyze these results in detail in the following sections.

Our model for  $R_{\rm ON}$  in (5) contains very specific dependencies on  $N_s$  (one explicit, but others implicit through the reduced surface potential). In order to compare this model with our measurements, we need to properly account for carrier degeneracy.  $\eta$  and the Fermi integrals can be calculated from

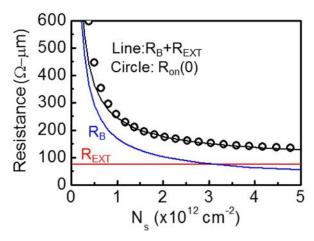

Fig. 6.  $R_{\rm ON}(0)$  from experiment as well as  $R_B$ ,  $R_{\rm EXT}$ , and the sum of  $R_B + R_{\rm EXT}$  based on modeling equations versus channel electron density.

the measured carrier density [17], [18], given an appropriate carrier effective mass. In our case, we select  $m_e^* = 0.041 m_o$ . Similar values have been obtained from tight-binding calculations and used in the modeling of InAs and InGaAs QW HEMTs [5], [19], [20]. The use of this value of  $m_e^*$  is further justified below.

Inserting the obtained  $\mathscr{F}_j(\eta)$  along with the value for  $v_{T0}$  ( $v_{T0}=2.65\times 10^7$  cm/s) that corresponds to the selected value of effective mass in (7) allows us to estimate  $R_B$  as a function of  $N_s$  in our devices. We can then add the necessary  $R_{\rm EXT}$  to provide the best possible match of our experimental measurements of  $R_{\rm ON}(0)$  from Fig. 4. The results of this procedure are shown in Fig. 6, where a unique value of  $R_{\rm EXT}=74~\Omega$ - $\mu$ m provides an excellent fit to all experimental results. Interestingly, this is an extraordinarily small value of  $R_{\rm EXT}$  which for our symmetric MOSFET architecture yields,  $R_s=R_d=1/2R_{\rm EXT}=37~\Omega$ - $\mu$ m. This underscores the excellent Mo-based ohmic contact technology and the efficacy of the contact-first self-aligned architecture of the devices used in this paper.

In Fig. 6,  $R_B$  is larger than  $R_{\rm EXT}$  for  $N_s < 3.1 \times 10^{12}$  cm<sup>-2</sup>. Over the entire range of  $N_s$  studied here, the ballistic resistance is never smaller than 70% of  $R_{\rm EXT}$ . The fact that the values of  $R_B$  and  $R_{\rm EXT}$  are comparable over the entire operational range of these devices cautions that the conventional external resistance extraction technique that ignores  $R_B$  significantly overestimates  $R_{\rm EXT}$  and the resulting contact resistivity. This further leads to an overestimation of extracted intrinsic transistor parameters by conventional methods [21], [22]. That is the case of channel mobility, intrinsic transconductance,  $g_{\rm mi}$ , and intrinsic output conductance,  $g_{\rm di}$ .

# IV. ANALYSIS OF MOBILITIES

Having determined the correct value for  $R_{\rm EXT}$ , the apparent mobility is obtained as a function of carrier density from (4)

$$\mu_{\rm app} = \frac{L_{\rm eff}}{(R_{\rm ON} - R_{\rm EXT})q N_s}.$$

(8)

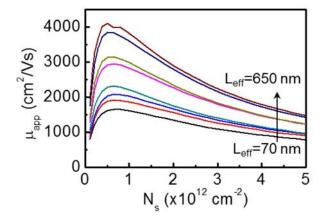

The extracted  $\mu_{app}$  versus  $N_s$  from (8) using the data set in Fig. 4 is shown in Fig. 7 for transistors with different

Fig. 7. Apparent mobility  $\mu_{\rm app}$  versus  $N_{\rm s}$  extracted for devices with different  $L_{\rm eff}$ .

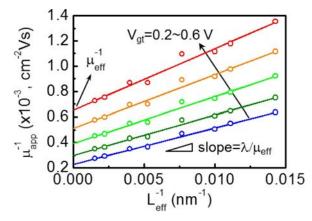

Fig. 8. Inverse of extracted apparent mobility versus inverse of effective gate length for the InGaAs MOSFETs at different gate overdrives.

$L_{\rm eff}$  values. We find that the mobility drops monotonically at moderate and high charge density for all gate lengths. At a given sheet carrier density, the mobility increases with gate length.

In order to analyze this result, we combine (1)–(3) to obtain

$$\frac{1}{\mu_{\rm app}} = \frac{1}{\mu_{\rm eff}} \left[ 1 + \frac{\lambda}{L_{\rm eff}} \right]. \tag{9}$$

This equation suggests that theory and experiments can be compared by plotting the inverse of the extracted apparent mobility against the inverse of the effective gate length for different gate overdrive voltages (i.e., channel charge). A straight line relationship is to be expected. This is done in Fig. 8 and indeed, the experimental results can be fitted well by straight lines at all gate voltages. From these fits, the long-channel effective mobility,  $\mu_{\rm eff}$ , can be extracted from the intercepts with the *y*-axis.  $\lambda$  can furthermore be obtained from the slope, which is equal to  $\lambda/\mu_{\rm eff}$ . The extracted values for  $\mu_{\rm eff}$  and  $\lambda$  are plotted against channel electron sheet density in Fig. 9(a) and (b). The extracted  $\mu_{\rm eff}$  in this way is completely equivalent to that obtained from the slope of  $R_{\rm ON}$  versus  $L_g$ , as shown in Fig. 5.

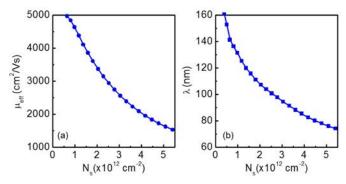

For low carrier concentration,  $\lambda$  is 160 nm and  $\mu_{\rm eff}$  is 5000 cm<sup>2</sup>/V · s. As  $N_s$  increases, both decrease. At  $N_s$  of  $5 \times 10^{12}$  cm<sup>-2</sup>,  $\lambda$  is down to 76 nm and  $\mu_{\rm eff}$  is 1600 cm<sup>2</sup>/V·s.

Fig. 9. (a) Long-channel effective mobility  $\mu_{\rm eff}$  and (b) MFP  $\lambda$  versus channel electron sheet density  $N_{\rm S}$ .

Fig. 10.  $\mu_{\rm eff}$  versus the expected dependence on  $\lambda$  and degeneracy. The data follows the model of (3) rather well.

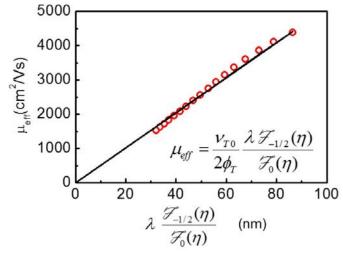

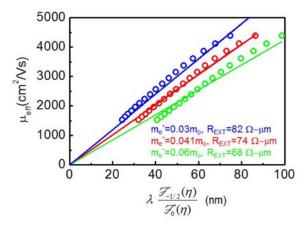

With the procedure followed here, we have separately obtained  $\mu_{\rm eff}$  and  $\lambda$ . We can then test the dependencies of the model of (3). Fig. 10 shows  $\mu_{\rm eff}$  versus the product of  $\lambda$  and the ratio of the Fermi integrals. A straight line through the origin is used to fit the data. The slope of the line represents  $v_{T0}/2\phi_T$ . The fit is fairly good and a  $v_{T0}$  value of  $2.65 \times 10^7$  cm/s is extracted. This is consistent with the effective mass and the thermal velocity used for the ballistic resistance calculation. The effect of choosing different effective mass values is examined in Appendix B.

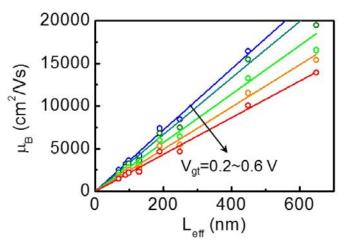

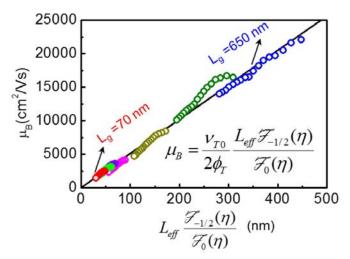

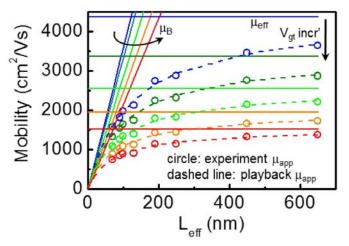

When  $\mu_{app}$  and  $\mu_{eff}$  are known,  $\mu_B$  can be extracted from (1). Alternatively,  $\mu_B$  can also be equivalently obtained from the extracted value of  $R_B$  in Fig. 6, since  $R_B$  and  $\mu_B$ are directly related:  $\mu_B = L_{\text{eff}}/(qN_sR_B)$ . Fig. 11 shows  $\mu_B$ versus  $L_{\text{eff}}$  for different values of  $V_{\text{gt}}$  using (1). At a given  $V_{\text{gt}}$ (corresponding to a single value of  $N_s$ ), the data can be fitted by a line crossing the origin. This agrees with the  $\mu_B$ dependence on  $L_{\text{eff}}$  in (2). As the gate overdrive increases,  $\mu_B$  decreases. This is expected from (2) since the ratio of Fermi integrals decreases as  $N_s$  and  $\eta$  increase (see graph in Appendix A). One can check the consistency of this entire data set by graphing the extracted  $\mu_B$ , as a function of the product of  $L_{\rm eff}$  and the ratio of the Fermi integrals. This, according to (2) should follow a straight line. Indeed, that is the case, as Fig. 12 indicates. The slope of the fitting line for Fig. 12 again yields  $v_{T0} = 2.65 \times 10^7$  cm/s.

Fig. 11. Ballistic mobility versus effective gate length at varying gate overdrives. The linear fits cross the origin.

Fig. 12.  $\mu_B$  versus  $L_{\rm eff}$  and degeneracy.

Fig. 13. Playback of apparent mobility calculated from extracted effective and ballistic mobilities, for different values of  $V_{\rm gt}$  and  $L_{\rm eff}$ . Good agreement with the experimental data is demonstrated.  $V_{\rm gt}$  is from 0.2 to 0.6 V.

To complete our analysis, we can use Matthiessen's law (1) to combine the extracted values of  $\mu_{\rm eff}$  and  $\mu_B$  and graph  $\mu_{\rm app}$  as a function of  $L_{\rm eff}$  and  $V_{\rm gt}$ . This is shown in Fig. 13. The horizontal solid straight lines are the effective mobility,  $\mu_{\rm eff}$ ,

which depends on  $V_{\rm gt}$  through  $N_s$ . The solid straight lines going through the origin are the ballistic mobility,  $\mu_B$ , which separately depends on  $L_{\rm eff}$  and  $V_{\rm gt}$ . The dashed lines show the calculation using (1), which agrees well with the experimental data (circles) at all values of  $V_{\rm gt}$  for all values of  $L_{\rm eff}$ .

#### V. CONCLUSION

In this paper, we present an analysis of the impact of ballistic transport on the linear characteristics ( $V_{ds} = 10 \text{ mV}$ ) of high-performance InGaAs MOSFETs. We use a model that includes ballistic transport under near-equilibrium conditions and accounts for carrier degeneracy in the channel. We show that the traditional technique of the external resistance extraction overestimates its value due to the presence of the gate length-independent ballistic resistance associated with ballistic transport in the channel. Our model allows us to extract an external resistance for our InGaAs MOSFETs with Mo contacts of  $\sim$ 74  $\Omega$ - $\mu$ m. We also extract the apparent mobility, the long-channel effective mobility, and the ballistic mobility, and show that the experimental results are consistent with our simple first-order model. Our study highlights the importance of correctly including ballistic effects and degeneracy when analyzing the characteristics of nanoscale InGaAs MOSFETs.

## APPENDIX

## A. Diffusive and Ballistic Mobilities

At low drain voltage, a QW-MOSFET operates under nearequilibrium conditions, in which the electron diffusion coefficient in the diffusive limit is given by [11, eq. (3.45)]

$$D_{\text{diff}} = \frac{\nu_T \lambda}{2}.$$

(A1)

The unidirectional thermal velocity of electrons,  $v_T$ , is related to the non-degenerate velocity,  $v_{T0}$ , through

$$v_T = v_{T0} \frac{\mathscr{F}_{1/2}(\eta)}{\mathscr{F}_0(\eta)} \tag{A2}$$

where  $v_{T0}$  in a 2DEG system with a single isotropic parabolic band is given by [17]

$$\nu_{T0} = \sqrt{\frac{2k_BT}{\pi m_e^*}} \tag{A3}$$

where  $m_e^*$  is the electron effective mass. For  $m_e^* = 0.041 m_0$ ,  $v_{T0} = 2.65 \times 10^7$  cm/s, as discussed in Section III.

Carrier diffusivity and mobility are related by the Einstein relationship including degeneracy is given by

$$\frac{D_{\text{diff}}}{\mu_{\text{eff}}} = \phi_T \frac{\mathscr{F}_{1/2}(\eta)}{\mathscr{F}_{-1/2}(\eta)}.$$

(A4)

Combining (A1)–(A4) yields the diffusive-limit effective mobility,  $\mu_{eff}$

$$\mu_{\text{eff}} = \frac{\nu_{T0}}{2\phi_T} \frac{\lambda \mathscr{F}_{-1/2}(\eta)}{\mathscr{F}_0(\eta)}.$$

(A5)

This equation relates the effective mobility and the MFP, and is consistent with [11, eq. (6.33)].<sup>1</sup>

$^{1}$ In [15] and [23], different expressions relating  $\lambda$  with  $\mu_{eff}$  are given, which are in error. The erratum [24] applies for both [15, eq. (A8)] and [23, eq. (D10)].

Fig. A1. Ratio of two Fermi-integral functions versus  $N_s$  for  $m_e^* = 0.041 m_0$ . This function introduces a dependence on carrier degeneracy in several equations in this paper.

Fig. B1. Effective mobility versus the product of MFP and the ratio of the Fermi integrals.  $R_{\rm EXT}$  values are matched for the respective effective masses. For  $m_e^* = 0.03m_0$  and  $m_e^* = 0.06m_0$ , increasing mismatch is observed when testing against (3).

The ballistic mobility  $\mu_B$  can be obtained by a similar approach, as is shown in [11].  $\mu_B$  follows a similar form as  $\mu_{\rm eff}$  except that its associated characteristic length is now the effective gate length  $L_{\rm eff}$ :  $\mu_B$  and  $R_B$  are related through the relationship shown in Section IV

$$\mu_B = \frac{\nu_{T0}}{2\phi_T} \frac{L_{\text{eff}} \mathscr{F}_{-1/2}(\eta)}{\mathscr{F}_0(\eta)}.$$

(A6)

The function  $\mathscr{F}_{-1/2}(\eta)/\mathscr{F}_0(\eta)$  appears in multiple equations and brings in the impact of degeneracy.  $\eta$  is uniquely determined by  $N_s$ .  $\mathscr{F}_{-1/2}(\eta)/\mathscr{F}_0(\eta)$  versus  $N_s$  is shown in Fig. A1 for  $m_e^* = 0.041 m_0$ .

#### B. Role of Assumed Effective Mass

The choice of effective mass impacts the value of the thermal velocity and the degree of carrier degeneracy for a given value of  $V_{\rm gt}$ . This propagates through our entire analysis. This paper assumes an effective mass of  $m_e^* = 0.041m_0$ , which was justified in Section III. This effective mass value results in the best matching between the experimental data and the expected dependence, as shown in Figs. 6, 10, and 12.

If different values of effective mass are used, we found that the quality of the matching between experiment and (3) is degraded. For example, using  $m_e^* = 0.03m_0$  or  $m_e^* = 0.06m_0$ , Fig. B1, which is similar to Fig. 10, shows that with the correspondingly adjusted values of  $R_{\rm EXT}$ , the quality of the fit calculated by (3) is somewhat decreased compared with  $m_e^* = 0.041m_0$ . Nevertheless, even with this  $\pm 25\%$  variation in  $m_e^*$ , the matching still appears reasonable. Therefore, our method cannot be used to pinpoint  $m_e^*$  with better than about  $\pm 25\%$  accuracy. On the other hand, as shown in the legend in Fig. B1, the extracted values of  $R_{\rm EXT}$ , which is one of the key aims of this paper, are relatively insensitive to the exact value used for the effective mass.

## ACKNOWLEDGMENT

The authors would like to thank insightful discussions with M. Lundstrom, M. Luisier, and A. Majumdar. The devices were fabricated at MIT's Microsystems Technology Laboratories and Scanning Electron-Beam Lithography Facility.

#### REFERENCES

- [1] J. A. del Alamo, "Nanometre-scale electronics with III–V compound semiconductors," *Nature*, vol. 479, no. 7373, pp. 317–323, Nov. 2011.

- [2] M. J. W. Rodwell et al., "Nanometer InP electron devices for VLSI and THz applications," in Proc. 72nd Annu. Device Res. Conf. (DRC), Jun. 2014, pp. 215–216.

- [3] S. W. Chang *et al.*, "InAs N-MOSFETs with record performance of  $I_{on}=600~\mu\text{A}/\mu\text{m}$  at  $I_{off}=100~\text{nA}/\mu\text{m}$  ( $V_{d}=0.5~\text{V}$ )," in *IEDM Tech. Dig.*, Dec. 2013, pp. 16.1.1–16.1.4.

- [4] J. Lin, D. A. Antoniadis, and J. A. del Alamo, "Novel intrinsic and extrinsic engineering for high-performance high-density self-aligned InGaAs MOSFETs: Precise channel thickness control and sub-40-nm metal contacts," in *IEDM Tech. Dig.*, Dec. 2014, pp. 25.1.1–25.1.4.

- [5] S. Rakheja, M. S. Lundstrom, and D. A. Antoniadis, "An improved virtual-source-based transport model for quasi-ballistic transistors— Part II: Experimental verification," *IEEE Trans. Electron Devices*, vol. 62, no. 9, pp. 2794–2801, Sep. 2015.

- [6] R. Landauer, "Spatial variation of currents and fields due to localized scatterers in metallic conduction," *IBM J. Res. Develop.*, vol. 1, no. 3, pp. 223–231, Jul. 1957.

- [7] S. Datta, Electronic Transport in Mesoscopic Systems. New York, NY, USA: Cambridge Univ. Press, 1997.

- [8] Y. Imry and R. Landauer, "Conductance viewed as transmission," Rev. Mod. Phys., vol. 71, no. 2, pp. S306–S312, Mar. 1999. [Online]. Available: http://dx.doi.org/10.1103/RevModPhys.71.S306.

- [9] K. Natori, "Ballistic metal-oxide-semiconductor field effect transistor," J. Appl. Phys., vol. 76, no. 8, pp. 4879–4890, Oct. 1994. [Online]. Available: http://dx.doi.org/10.1063/1.357263.

- [10] M. S. Shur, "Low ballistic mobility in submicron HEMTs," IEEE Electron Device Lett., vol. 23, no. 9, pp. 511–513, Sep. 2002.

- [11] M. Lundstrom and C. Jeong, Near-Equilibrium Transport: Fundamentals and Applications, 1st ed. Singapore: World Scientific, 2013.

- [12] A. Majumdar and D. A. Antoniadis, "Possible observation of ballistic contact resistance in wide Si MOSFETs," in *Proc. 70th Annu. Device Res. Conf.*, Jun. 2012, pp. 197–198.

- [13] J. Lin, X. Zhao, T. Yu, D. A. Antoniadis, and J. A. del Alamo, "A new self-aligned quantum-well MOSFET architecture fabricated by a scalable tight-pitch process," in *IEDM Tech. Dig.*, Dec. 2013, pp. 16.2.1–16.2.4.

- [14] J. Lin, D. A. Antoniadis, and J. A. del Alamo, "A CMOS-compatible fabrication process for scaled self-aligned InGaAs MOSFETs," in *Proc.* CS MANTECH, 2015, pp. 239–242.

- [15] J. Wang and M. Lundstrom, "Ballistic transport in high electron mobility transistors," *IEEE Trans. Electron Devices*, vol. 50, no. 7, pp. 1604–1609, Jul. 2003.

- [16] A. A. Kastalsky and M. S. Shur, "Conductance of small semiconductor devices," *Solid State Commun.*, vol. 39, no. 6, pp. 715–718, Aug. 1981.

- [17] F. Assad, Z. Ren, D. Vasileska, S. Datta, and M. Lundstrom, "On the performance limits for Si MOSFETs: A theoretical study," *IEEE Trans. Electron Devices*, vol. 47, no. 1, pp. 232–240, Jan. 2000.

- [18] S. Rakheja, M. S. Lundstrom, and D. A. Antoniadis, "An improved virtual-source-based transport model for quasi-ballistic transistors—Part I: Capturing effects of carrier degeneracy, drain-bias dependence of gate capacitance, and nonlinear channel-access resistance," *IEEE Trans. Electron Devices*, vol. 62, no. 9, pp. 2786–2793, Sep. 2015.

- [19] M. Luisier, N. Neophytou, N. Kharche, and G. Klimeck, "Full-band and atomistic simulation of realistic 40 nm InAs HEMT," in *IEDM Tech. Dig.*, Dec. 2008, pp. 1–4.

- [20] M. Luisier, private communication, Sep. 2015.

- [21] S. Y. Chou and D. A. Antoniadis, "Relationship between measured and intrinsic transconductances of FET's," *IEEE Trans. Electron Devices*, vol. 34, no. 2, pp. 448–450, Feb. 1987.

- [22] S. M. Sze and K. K. Ng, Physics of Semiconductor Devices, 3rd ed. New York, NY, USA: Wiley, 2006.

- [23] A. Rahman and M. S. Lundstrom, "A compact scattering model for the nanoscale double-gate MOSFET," *IEEE Trans. Electron Devices*, vol. 49, no. 3, pp. 481–489, Mar. 2002.

- [24] A. Rahman and M. S. Lundstrom, "Erratum: A compact scattering model for the nanoscale double-gate MOSFET [Mar 02 481-489]," *IEEE Trans. Electron Devices*, vol. 62, no. 7, p. 2367, Jul. 2015.

**Jianqiang Lin** (S'08) received the B.Eng. (Hons.) and M.Eng. degrees in electrical engineering from the National University of Singapore, Singapore, in 2007 and 2009, respectively, and the Ph.D. degree from the Massachusetts Institute of Technology, Cambridge, MA, USA, in 2015.

He is currently a Post-Doctoral Associate with the Massachusetts Institute of Technology.

Yufei Wu received the B.S. degree in electrical engineering from The Pennsylvania State University, State College, PA, USA, in 2012, and the M.S. degrees in electrical engineering from the Massachusetts Institute of Technology, Cambridge, MA, USA, in 2014, where she is currently pursuing the Ph.D. degree in electrical engineering.

Her current research interests include modeling and testing reliability of GaN FETs.

Jesús A. del Alamo (S'79–M'85–SM'92–F'06) received the Telecommunications Engineer degree from the Polytechnic University of Madrid, Madrid, Spain, in 1980, and the M.S. and Ph.D. degrees in electrical engineering from Stanford University, Stanford, CA, USA, in 1983 and 1985, respectively.

He has been with the Massachusetts Institute of Technology, Cambridge, MA, USA, since 1988, where he is currently a Donner Professor of Electrical Engineering.

**Dimitri A. Antoniadis** (M'79–SM'83–F'90–LF'14) received the B.S. degree in physics from the National University of Athens, Athens, Greece, in 1970, and the M.S. and Ph.D. degrees in electrical engineering from Stanford University, Stanford, CA, USA, in 1972 and 1976, respectively.

He joined the Massachusetts Institute of Technology, Cambridge, MA, USA, in 1978, where he is currently the Ray and Maria Stata Professor of Electrical Engineering.