# **Characterizing the Bilayer TFET**

Mitchell Maciorski<sup>1</sup>, Jared Carter<sup>2</sup>, Eli Yablonovitch<sup>2</sup> <sup>1</sup>Moorpark College, <sup>2</sup>University of California, Berkeley

2013 Transfer-to-Excellence Research Experiences for Undergraduates Program (TTE REU Program)

## Abstract

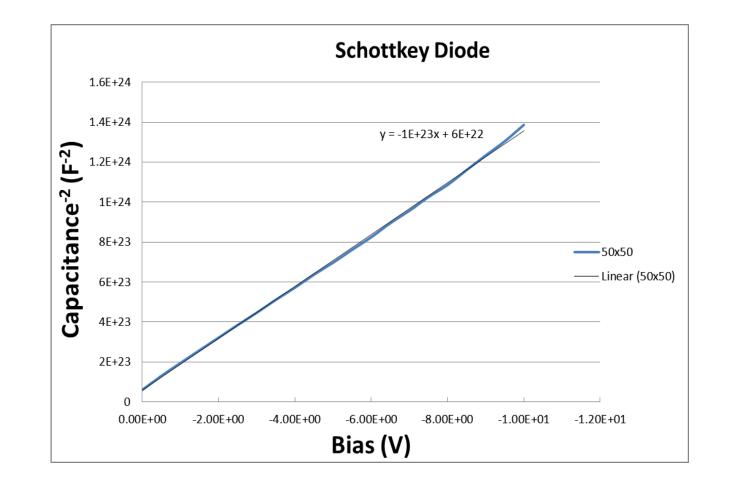

The bilayer tunneling field effect transistor (TFET) is a transistor which utilizes electron tunneling as its switching mechanism. It is currently being investigated as a low power alternative to the conventional MOSFET. Here, the electrical properties of an incomplete bilayer TFET are examined by utilizing a MEMS Cascade probe station and two semiconductor parameter analyzers. Through measurement of test devices such as MOS capacitors, Schottkey Diodes, and P-N Junctions, device characteristics such as sheet resistance, contact resistivity, oxide current leakage, oxide breakdown voltage, and dopant concentrations were determined. These results display device gate functionality, operating voltage limits, and leakage current density.

| Introduction                                                                                                                                                                        | Results                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

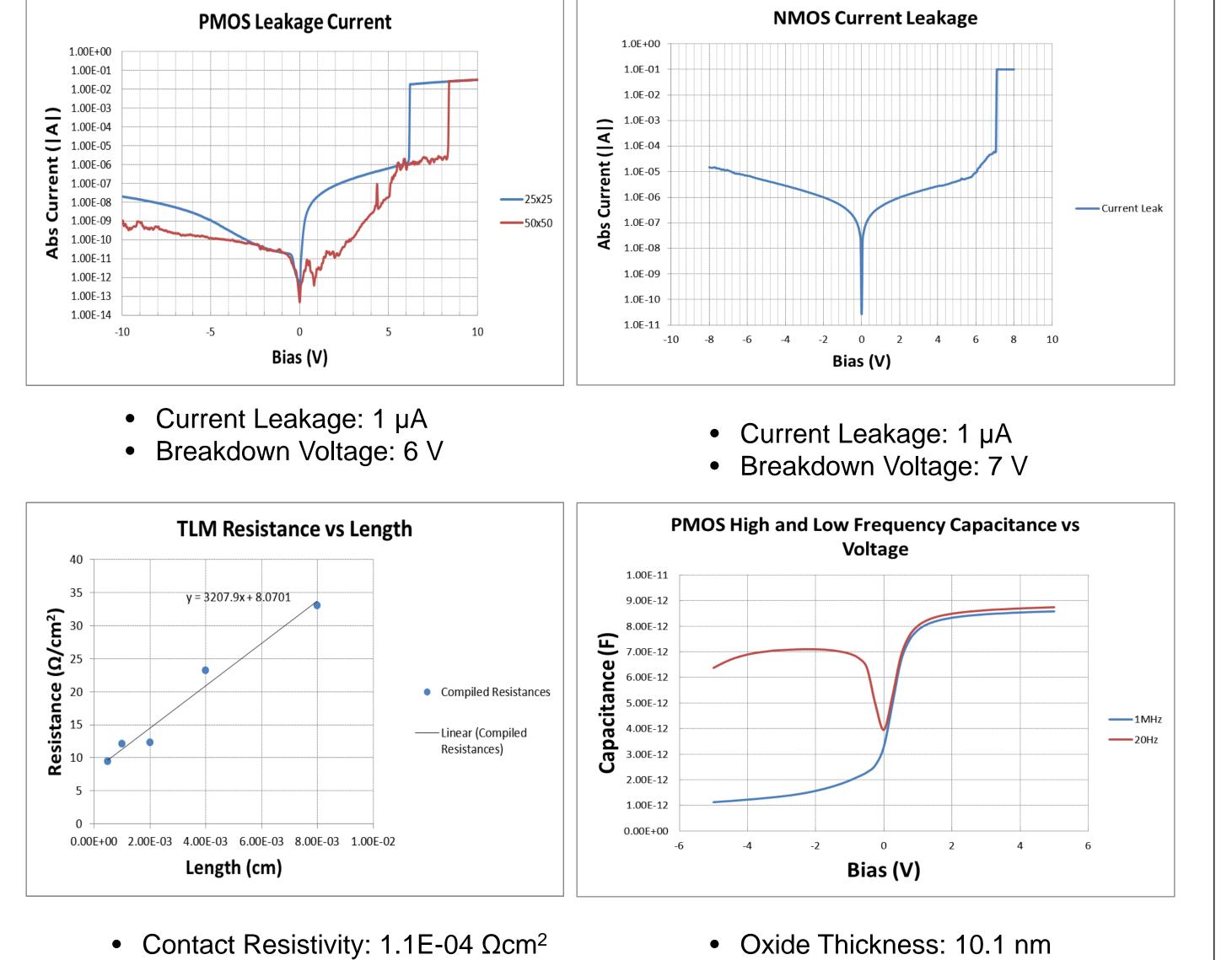

| Power consumption of electronic devices has been subject to recent scrutiny. In response, it was proposed that a new class of transistors called tunneling field effect transistors | PMOS Leakage Current NMOS Current Leakage |

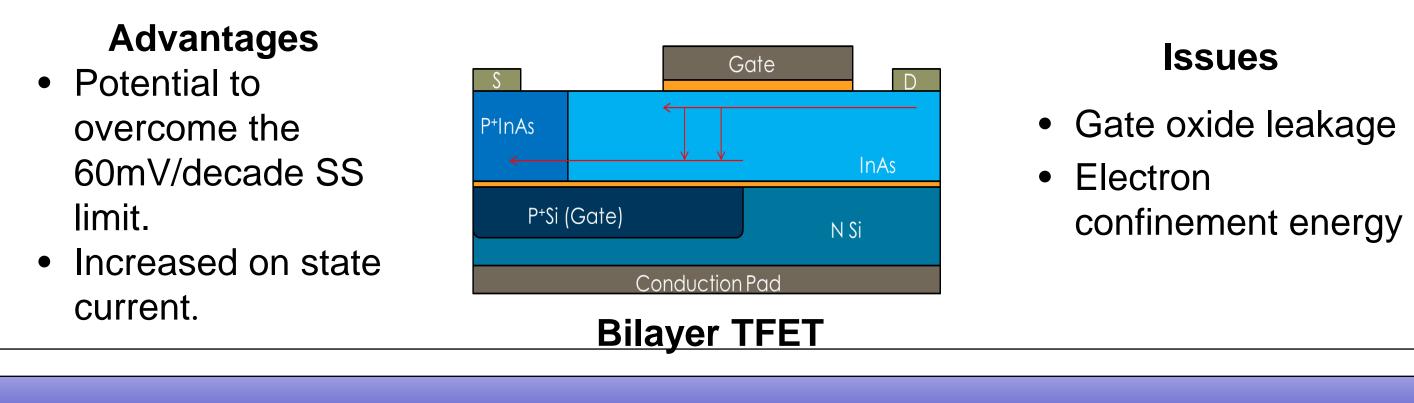

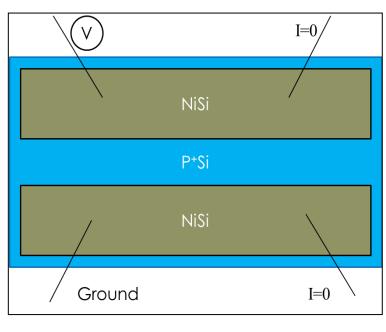

(TFETs) could be utilized. Simulations of proposed TFET designs showed promise of overcoming the thermal subthreshold swing (SS) limit of MOSFETs. The bilayer TFET is just one of a handful of proposed TFET designs. It is much different from the conventional transistor because it has a very thin conduction body, two offset gates, and current is passed in an unusual path because of vertical band to band tunneling (BTBT).

### **Measurement Tools**

- Mems Cascade Probe Station

- HP 4284A Semiconductor **Parameter Analyzer**

- Compares Capacitance to applied Voltage

- Agilent 4155C Semiconductor **Parameter Analyzer**

- Compares Current to applied Voltage

• 2 Probe application

- Sheet Resistance: 31.4  $\Omega/cm^2$

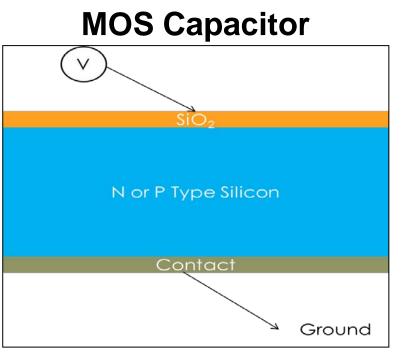

- Oxide Capacitance: 3.7E-12 F

Tools measure test structures on the edge of the device.

### **4 Point Probe Measurement**

- Measures total resistance while bypassing internal resistance

- Compares resistance to length between conduction pads. Useful in deriving sheet resistance and contact

#### resistivity **PN** Junction

- 2 probe measurement

- Measures the flow of electrical current through a PN junction

- Useful for determining PN reverse bias breakdown voltage

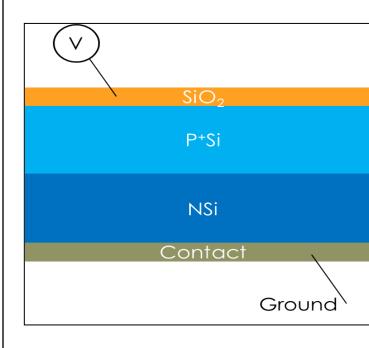

- Measure Capacitance and Current

- Useful in determining oxide integrity, oxide thickness, and density of interface traps

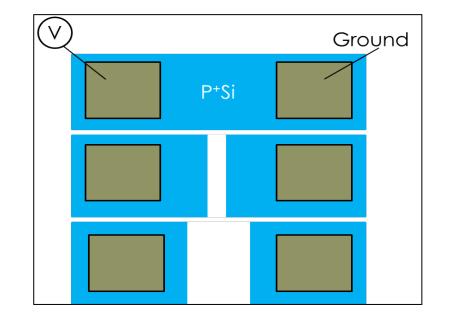

#### **Diffusion Test**

- 2 probe measurement

- Measures current flow through a short and two spaced substrates.

- Checks how much dopants diffused during annealing

**Jared Carter** Eli Yablonovitch E3S Center

- Built-in Voltage: 0.4 V

- Dopant Concentration: 1.3E17 cm<sup>-3</sup>

## Conclusions

- Maximum operating voltages have been determined to be 6 or 7 volts

- PN junction will function properly as a bottom gate.

- Gate oxides will leak current

- Development of the device will continue.